Author: Chetan Khona

Xilinx All Programmable SoCs and 7 Series FPGAs not only provide the broadest range of capabilities for today's Industrial Internet of Things (IIoT) platforms, but also provide maximum flexibility for future growth. Achieve the highest return on investment and the lowest total cost of ownership throughout the lifecycle of an industrial system.

summary

This white paper uses industrial communications, network security, and edge computing (from simple data optimization to machine learning) as an example to highlight the suitability and benefits of the Xilinx Zynq-7000 SoC and Zynq UltraScale+ MPSoC for industrial IoT embedded systems. These devices combine ARM application processors with FPGA logic (programmable hardware), peripherals, and other embedded modules to give users the ideal balance between software intelligence and hardware optimization for their systems.

This white paper explores the life cycle of industrial equipment and how it can be combined with software and programmable hardware to fundamentally improve the functionality of the system in the short term, while extending the life of the system in the rapidly changing industry of the Internet of Things market. This white paper will also introduce software tools that assist in the distribution of functionality between software and programmable hardware, while demonstrating the business risks and costs of not using the All Programmable solution.

IT-OT fusion method

Industrial Internet of Things (IIoT) refers to a multi-dimensional, tightly coupled system chain involving edge devices, cloud applications, sensors, algorithms, security, confidentiality, a large number of protocol libraries, human machine interfaces (HMIs), and other interoperable elements. Some people describe the IIoT vision as a convergence of operational technology (OT) and information technology (IT), but in fact the goal is far-reaching. The time sensitivity of OT applications and the data intensiveness of IT applications require that all of these elements be integrated to perform critical tasks on time and reliably. But there is a conflict with another key requirement (ie life cycle). The life cycle ensures the return on investment of these IIoT systems from system suppliers and their customers. Significant progress is being made in a series of underlying technologies such as analysis, machine learning, and network security for the IIoT system. However, modifications or upgrades are made during the extended lifecycle, and this tight integration requirement can cause unnecessary chain reactions to the rigorous timeliness of these systems.

The most common way to address this challenge is to find an embedded electronic component that can be used as the core of the IIoT edge system – with the best specifications available to handle unexpected situations. The edge system refers to the decisive embedded communication and real-time control engine located at the edge of the network, closest to the physical factory and other industrial environments (such as motion controllers, protection relays, programmable logic controllers, etc.). The gigahertz clock frequency, increased memory capacity, increased number of input/output ports, and the latest encryption engine seem to provide solutions for future needs that are not yet known. But when dealing with the time scale of industrial equipment, because its key subsystems work on a time scale of hundreds of milliseconds (or less), they need to work in factories and remote locations for decades, relying only on advanced multi-core embedded processing. The expansion of the device in the IIoT field can only be regarded as an imagination at most. In the worst case, this is a short-sighted approach that leads to a series of difficult and costly marketing and engineering trade-offs, and the main purpose of trade-offs is to manage the functional timing issues caused by performance bottlenecks. In view of the time scale involved, there is a need for a higher degree of freedom of expansion at the edge of the IIoT. This extended freedom can be released by using programmable hardware to enhance the software running on the embedded processor core. This more consistent approach makes it easy to manage determinism, latency, and performance, eliminating interference within the IT and OT domains and within the OT domain subsystem.

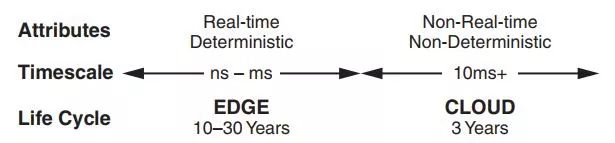

Figure 1: Time scale, attributes, and life cycle of a typical IIoT system

In parallel, processors that provide features such as hardware virtualization can deliver sustainable value, which not only allows architects to integrate new guest operating systems, but also provides the level of automation and isolation required. It also provides features that are always useful, such as time-invariant features like memory protection (parity, or best error correction code [ECC]).

The use of dedicated hardware to enhance the static processor architecture, to achieve the division of labor, let each hardware perform its duties, this is not a new model for the embedded electronics industry. It is also important to note that tasks and labor divisions are automatically adjusted over time. For example, the latest predictive maintenance algorithm requires more sensor inputs than the previous number of inputs. Let the hardware be responsible for the incremental calculations to maintain the overall load and the cycle time of the processing subsystem (which is the most important). This flexible performance brings huge benefits to customers who purchase and install systems and system vendors who receive multiple value-added software service revenue streams from the device over the next few decades.

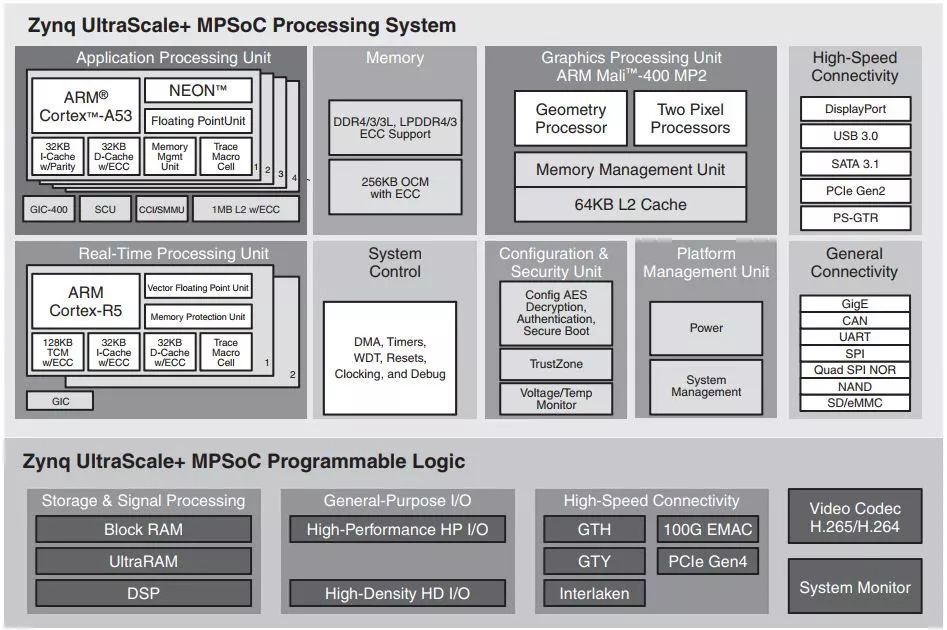

In the context of choosing an IIoT edge platform that can adapt to the impact of market trends over time, this white paper focuses on the three key application areas that make up the IIoT foundation (ie connectivity, network security, and edge computing). It is extremely important to have a highly flexible, scalable IIoT platform that can handle both OT and IT technologies. The All Programmable SoC (Complete Programmable System-on-Chip) is an ideal solution for both software programmable and hardware programmable features. This white paper also covers two technical topics related to All Programmable SoCs: software-defined hardware and the comparison of All Programmable SoCs with secondary FPGAs that separate embedded processors. The Zynq-7000 SoC and Zynq UltraScale+ MPSoC series from Xilinx are dedicated to IT and OT tasks. See Figure 2.

Figure 2: Zynq UltraScale+ block diagram

Connection: From existing standards to future agreements

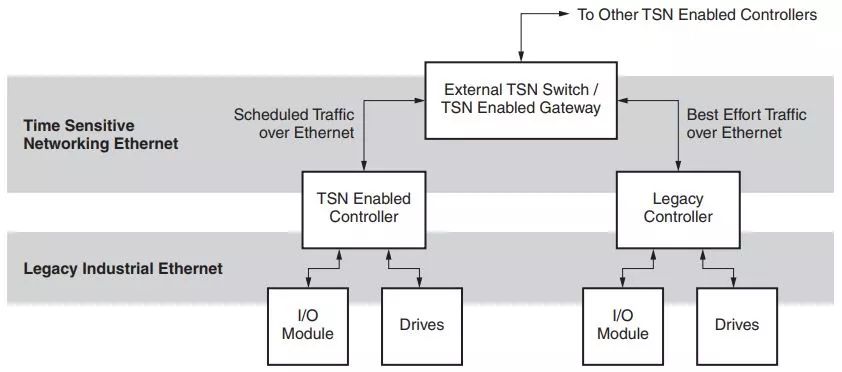

The connection in the era of IIoT is moving towards a streamlined approach, but this transformation brings new complexity. Edge and system-level protocols such as the OPC Foundation's Open Platform Communications Unified Architecture (OPC-UA) and Real-Time System Data Distribution Service (DDS) are gaining momentum in their respective applications. Both of these can be greatly benefited by the rise of time-sensitive networks (TSNs). This is a deterministic Ethernet transport that manages mixed critical flows. TSN can effectively implement a unified network protocol vision across the entire edge network and most of the IIoT network, as it can support various levels of scheduled traffic with best-effort traffic. TSN is an evolving and evolving standard that promotes standard compliance for dedicated chipsets (such as ASICs or ASSPs) before all aspects of the standard and final market-specific conditions are settled. Similarly, attempting to add TSN support to an existing controller that manages real-time data through a purely software approach can at least lead to unpredictable timing behavior. This may cause deterioration in interrupt response, delayed memory access time, and the like. Ultimately, this won't be a reasonable solution because TSN requires a form of time-awareness that is not yet available in current processors. But even if TSN is not integrated in the same device (to manage control functions, such as endpoints), if an external TSN switch is integrated into the system, switches connected to multiple endpoints are likely to be able to provide Ethernet for controllers that support non-TSN. Backward compatibility support. The goal is to integrate the TSN into the endpoint to minimize the impact on the timing of the control functions while parallelizing the scheduled traffic with the best-effort traffic. See Figure 3.

Figure 3: TSN topology and advantages

Integrating the All Programmable TSN implementation into the controller minimizes the impact of changes by enabling bandwidth-intensive and time-critical functions in hardware without significant impact on software timing. Designers can implement pure endpoints or bridge endpoints using a fully standards-compliant TSN optimization implementation developed internally by Xilinx. Whether upgrading a controller designed with All Programmable SoCs from standard Ethernet to TSN or designing new controllers using the evolving TSN standard, Xilinx's All Programmable approach not only allows designers to make changes when they make changes Try to avoid impacting critical timing while still meeting future needs (as opposed to ASICs and ASSPs).

Also worth considering is an alternative, but equally common use case. Because IIoT is not a new industry, it still needs to support the large number of traditional industrial protocols used in this industry before and now in this segmentation state. Most new SoCs do not support even a significant portion of these protocols. Therefore, the number of network interfaces may exceed the I/O capabilities of most of these fixed SoCs. In contrast, systems created with Xilinx's All Programmable SoC can meet customer customization requirements, such as supporting legacy protocols and their associated I/O connections. Regardless of whether the protocol requires 250μs or 64μs cycle time, these industrial communication controllers can eliminate the cost of additional devices by using a full package and hardware offload implementation without causing software solutions that can cause mainstream software and firmware. side effect.

Whether using TSN, traditional industrial protocols, or the most common mix of old and new, Xilinx offers any connection with design determinism.

Cybersecurity: hardened and adaptable to future threats

For the broad topic of cybersecurity, the IIoT thought leader adopts a “defense in depth†approach. Defence defense is a multi-layered form of security that begins with the supplier's supply chain, up to the end user's enterprise and cloud applications, and even extends to what the software might connect to. In this section we will introduce the chain of trust for embedded electronic devices deployed on the edge of the IIoT. As the network extends to the analog-digital boundary, data must be secured as long as it enters the digital domain. Deep Defense Security requires a strong hardware root of trust, enabling security and measurement boot operations and runtime security through hardware, operating system and software isolation, and secure communications. The operation of independently verifying the certificate through a trusted remote authentication server, a certificate authority, etc., should be deployed through the chain.

In the case of an expected increase in the frequency of cybersecurity attacks, security is not static, but is constantly evolving. For example, since 1995, five major changes have been made to the Transport Layer Security (TLS) Secure Messaging Protocol, and many more improvements are forthcoming. IIoT system vendors and their customers need to know how to mitigate long-term security risks while maximizing the longevity and utilization of high-cost assets. Encryption algorithms that lay out protocols such as TLS are generally implemented in hardware, but as IT-OT convergence evolves, these IT-side changes can adversely affect time-critical OT performance. To mitigate this impact, some software architecture tools such as hypervisors and other isolation methods are now available. After years of product deployment in the field, these software concepts can also be combined with the ability to use programmable hardware offload and support for new encryption features not yet defined. This approach provides a stronger risk aversion program that avoids costly recalls, patches, and possible legislative threats.

Software defined hardware

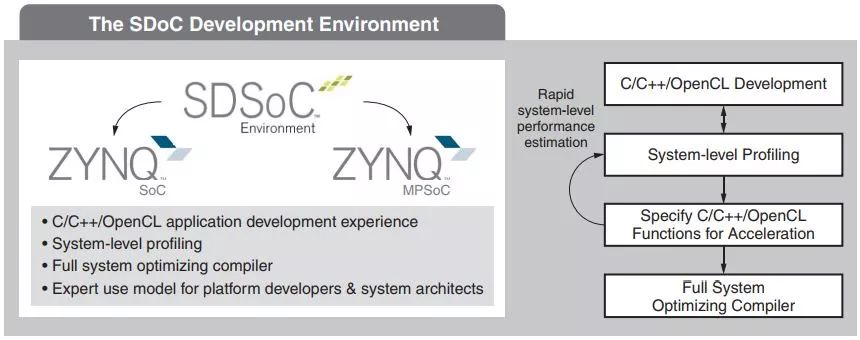

As mentioned in the section "Network Security: Hardened and Ability to Adapt to Future Threats", hardware offloading is not just the support of All Programmable SoC programmable hardware. Achieving the entire vision requires software automation that optimizes this technology. Tools like the SDSoCTM development environment allow users to write C/C++/OpenCL and other growing languages, partitioning all or part of the functionality into programmable hardware or software. The SDSoC development environment also generates a data movement engine and infrastructure between the processor and programmable hardware. In 2015, the SDSoC tool used the Advanced Encryption Standard (AES)-256 algorithm to increase display performance by up to 4x when moving algorithms to programmable hardware. "Using SDSoC to Accelerate AES Encryption" in Xcell Software.

The benchmark is focused on exploring the best balance between software intelligence and programmable hardware optimization. However, this tool can also completely offload this functionality to programmable hardware. Similarly, with the hardware acceleration engine, the motor control loop convergence time can be 30-40 times better than a pure software implementation. See Figure 4.

Figure 4: SDSoC design environment design flow

Edge computing: scalable, low cost and real time

Like communication and security, edge computing is evolving in many directions. The computing power of the cloud runs on data streams released by previously inaccessible systems, providing users with unprecedented insights that are unprecedented or incomprehensible. This establishes an expected or desktop chip that can be used as a new baseline. Just as relying on GPS real-time navigation systems would make most highway maps out of date, buyers and users of industrial equipment have different expectations for feedback from their IIoT systems. Driven by the following three factors, the trend is to push the generation of these insights from the cloud to the edge:

• Apply insights as fast as possible in the round-trip loop from edge to cloud

• The cost of sending (in many cases) large amounts of data to the cloud

• Security, reliability and privacy issues in sending data to the cloud

Some industry trends should not be seen as absolute. To solve some of these security and privacy issues, even pre-processing data locally and then sending optimized obfuscated data to the cloud can bring huge benefits. The simplest example is the application of a low pass or averaging filter to time series data on the controller responsible for controlling the machine. The result is both reduced number of data points sent to the cloud and outliers. With programmable hardware, you can optimize these features

Applied to the data as it flows out of the machine. The most efficient data processing is achieved compared to using complex memory transactions. This is because memory transactions can affect the response time of making any possible decisions based on the data. This example can be expressed as a single data stream from a single sensor, but in reality many industrial systems consist of hundreds or even thousands of parallel data streams. The number of connections magnifies the problem, as well as the value of the solution provided by the programmable hardware through various sensor fusion techniques and on-chip analysis.

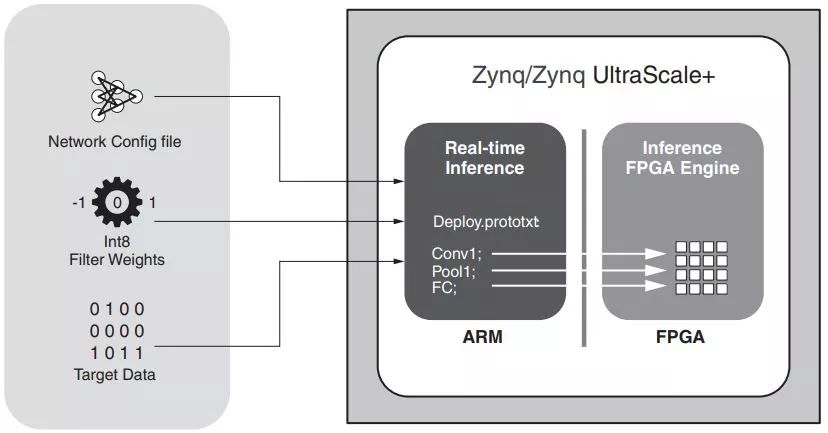

In the example described here, intelligence is embedded in the controller, local adjustments are made to time-sensitive feedback items, and data with less time criticality is pushed to the cloud in a compressed format. This is the best example of complementing the edge and the cloud. This description of embedded intelligence and edge-cloud collaboration can also be applied to machine learning on the edge, a topic of increasing importance in the IIoT space. Machine learning — including neural network-based machine learning inference and deployment, and regression and other classic methods—is extremely suitable for energy-efficient, customizable, and massively parallel computing architectures made up of programmable hardware. For this reason, programmable hardware-based accelerator cards are widely used in the cloud. The same All Programmable technology is available at the edge, providing the lowest latency, power and cost for multi-sensor machine learning applications. Because All Programmable technology can efficiently support all the fundamental aspects of IT-OT convergence while providing first-class capabilities in emerging areas, the technology can cover the widest range of IIoT applications. For example, combining motor control, machine vision, network communication, functional safety, network security and other applications with edge analysis and machine learning is an expected use case for All Programmable technology in IIoT. By using tools such as the SDSoC development environment with support libraries, users can implement a large number of algorithms in the device by taking up a portion of the resources of the smallest All Programmable device. See Figure 5.

Figure 5: Machine learning inference process for Zynq-7000 and Zynq UltraScale+ SoC

Auxiliary FPGA for traditional processors

To achieve a wide range of IT-OT capabilities, the IIoT edge platform is the All Programmable SoC. These devices offer the integration benefits described earlier while reducing power consumption and cost. In a real-world environment where there is already a previous architecture, such as the case of traditional code dedicated to traditional embedded processors, there is another option. In this case, some of the advantages described above can still be exploited by using purely programmable hardware devices called FPGAs. The FPGA operates as an auxiliary device that can interface easily with the main embedded processor. These FPGAs act as coprocessors for the main embedded processor, offering the option of implementing a compact microprocessor or micro coprocessor (such as Xilinx MicroBlazeTM). These soft processors (built with programmable hardware) support multiple operating systems and real-time operating systems. With these options, evolving or time-critical features can also be offloaded in traditional system environments. Xilinx's All Programmable portfolio, such as FPGAs and SoCs, not only enables long-life, high-availability chips that can be used over a wider temperature range, but also reconfigures all or part of the device, even during operation. in this way. Multi-FPGA options are also available in the case of shared package compatibility, making it easy to take platform measures. The two-chip approach lacks high bandwidth between the processor and the FPGA compared to the All Programmable SoC. This high-bandwidth and number of connections within a single-chip SoC facilitates the dynamic division of labor between hardware and software (the preconditions of the previous example), a feature that is unmatched by a two-chip solution. Even with these limitations, the value of programmable hardware is large enough for more and more embedded processors to promote dedicated FPGA interfaces in their data sets (generally built to PCIe, SPI, QSPI, etc.).

Hardware and software programmability for life in the new industrial era

The use of electrification industrial control systems has been around for more than a hundred years. Just as some people refer to IIoT as the fourth industrial revolution, not only the available technology and the tasks required to be completed have changed, but the speed of development of the entire industry has also accelerated with the speed of change. At present, IT-OT tasks have been deepened and expanded over time, and new technologies for the building blocks of the IIoT edge platform have emerged to enable them to handle these tasks well. All Programmable SoCs, such as Zynq-7000 and Zynq UltraScale+ devices, use software and hardware programmability to keep assets long-lived compared to traditional embedded architecture building blocks used in the last two or three decades. The approach of using different embedded processors for each endpoint product, regardless of the connection to the same cloud infrastructure, is a way to fail because about 75% of the cost of the IIoT system development is with the cloud. It is closely related to embedded software development. For system vendors, the most important thing is to create value for their R&D time and capital through software services, rather than redeveloping communication interfaces, security infrastructure, control loop timing, data analysis algorithms, and more. The FPGA approach offers many of these advantages for vendors who have to deal with traditional processors. The All-Programmable SoC approach helps maximize the available options and is key to increasing the return on investment for industrial system suppliers and their customers.

in conclusion

In summary, this white paper focuses on how Xilinx All Programmable SoCs and FPGAs maximize the return on investment (ROI) for system vendors and their customers by:

• The long-term availability of Xilinx All Programmable SoCs and FPGAs, combined with their inherent hardware and software programmability, enables on-site updates to avoid the risk of not complying with new IIoT standards and trends.

• Provides scalability for system vendor platforms through multiple Xilinx device families, reducing total cost of ownership with a comprehensive product line

• Integrate multiple IIoT functions from IT domains and OT domains into a single, highly flexible, low latency, energy efficient device

UV Screen Protector,UV Curing Machine,UV Curing Screen Protector

Shenzhen Jianjiantong Technology Co., Ltd. , https://www.jjthydrogelprotector.com