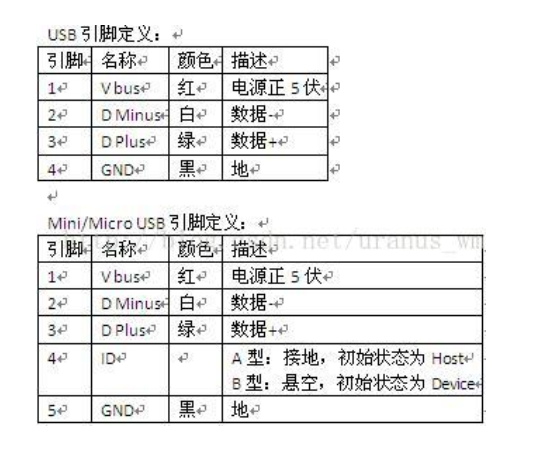

A USB pin is generally four lines, defined as follows:

To support OTG function, the mini/micro usb interface expands an ID pin (pin 4)

If the device ID is grounded, the initial state is Host. For example, when the PC and the OTG device are supported as the master device.

B device end ID pin is floating, the default pull-up is high, the initial state is Device, for example, U disk and OTG device support slave device

1. For mobile devices to support OTG, the internal ID pin needs to be pulled up by default to high.

2. VBUS is an input and output bidirectional pin. For Device is the power supply input pin; for the Host need to string a 5V power output to the device.

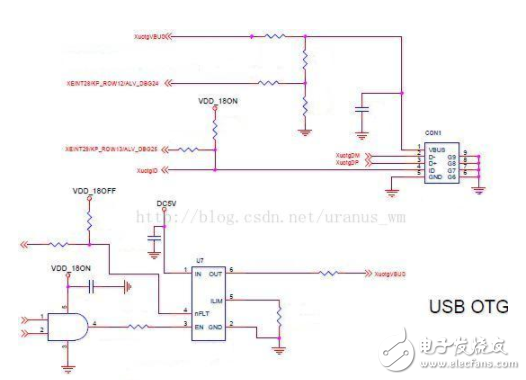

Two USB plug-in detection process, see the following simple circuit, Samsung Exynos4412 platform:

Circuit Description: CON1 is a micro usb connector, VBUS is connected to the system XuotgVBUS pin, and an interrupt output pin is provided to XEINT28

At the same time, an external DC5V is also output to the XuotgVBUS through the control chip, which is used as a host to supply external power.

The ID pin pulls up 1.8V as Host/Slave detection, while providing another interrupt input pin to XEINT29

The device supports OTG. The following describes the discovery process of the device:

When plugged into the PC port from the device:

1. The system detects the rising edge of XEINT28 on VBUS to trigger the interrupt, because there will be a 5V from the VBUS on the PC side, enter the interrupt processing function to further confirm the ID pin status, the ID pin is low, the status is wrong, and the ID pin is high to indicate the device. Should switch to slave mode

2. Invoke the usb gadget to enable vbus and enable the PHY according to the device mode. The gadget registers an SPI soft interrupt IRQ_USB_HSOTG during the probe to respond to data reception.

3. Turn on usb clk and enable PHY. At this time, external 5V power supply system XuotgVBUS, gadget receives IRQ_USB_HSOTG interrupt request to restart OTG core

4. A high-level pulse is generated on the USB DP (DP for high-speed devices and DM for low-speed devices). At this time, the PC recognizes that a USB device is plugged in, and Windows prompts the user.

5. Follow-up is the process of SETUP, GET DISCRIPTOR

When the master device is discovered as a device plugged in:

1. The system detects that the XEINT29 falling edge trigger interrupt on the ID pin (actually the inserted fourth port of the usb public port is directly connected to the fifth foot ground), enters the interrupt processing, and switches to the master device mode.

2. Turn off the interrupt, enable DC5V to power on VBUS, wake up ehci and ohci

3. The usb core registers a kernel thread named khubd during kernel initialization, and khubd monitors the port event. (The actual process I understand is that after the power is supplied from VUBS, a high-level pulse will be generated on the DP or DM.

Ehci recognizes the device insertion after receiving the pulse signal, just understanding, this is not verified)

3. khubd gets the port, speed is passed to ehci, then is the usb SETUP, GET DISCRIPTOR process

USB C Hub

Usb C Hub,4 Ports 3.0 Type C Hub,Adapter For Macbook Hub,Slim External 4 Port Usb3.0 Hubs

Shenzhen GuanChen Electronics Co., Ltd. , https://www.gcneotech.com